-

CycloneIII设计向导 第一篇:芯片选型 1.考虑器件的资源,包括LE,ram资源,硬件乘法器,PLL,全局时钟网络等。 总体来说,对于FPGA设计,资源一定要留有余量,否则最后的时序收敛会比较困难。我认为使用80%左右是比较合适的。对于资源使用量在95%以上的设计,除了时序收敛,可能还会遇

-

TimeQuest就一定要搞定——时序分析基本公式 以下内容译自 Quartus II Version 7.0 Handbook , Volume 3 : Verification 的 6-28 : Clock Analysis 部分。 riple TimeQuest 静态时序分析的对象包括:寄存器和寄存器之间的路径、 I/O 之间、 I/O 和寄存器之间

-

引言 分频器 在 CPLD / FPGA 设计中使用频率比较高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源 ,但是对于要求奇数倍分频(如3、5等)、小数倍(如2.5、3.5等)分频、占空比50%的应用场合却往往不能满足要求。硬件工程师希望有一种灵活的设计方法,根据需要,在实验室就能设计分频器并马上投入使用

-

这是一个在逻辑设计中注意事项列表,由此引起的错误常使得设计不可靠或速度较慢,为了提高设计性能和提高速度的可靠性,必须确定设计通过所有的这些检查。 可靠性 1. 为时钟信号选用全局时钟缓冲器BUFG! 不选用全局时钟缓冲器的时钟将会引入偏差。 2. 只用一个时钟沿来寄存数据 使用时钟的两个

-

摘 要 本文首先建立了单信道的软件无线电数学模型,分析比较了FPGA、ASIC以及DSP设计方式的优缺点,并深入研究了FPGA技术在软件无线电中的应用。 关键词 现场可编程门阵列 上/下变频器 DA算法 1 引言 软件无线电的基本思想是:A/D、D/A变换器尽可能地接近天线,用软件来

-

1 引 言 多电平正交幅度调制MQAM(Multilevel QuadratureAmplitude Modulation)是一种振幅和相位相结合的高阶调制方式,具有较高的频带利用率和较好的功率利用率。因为单独使甩振幅和相位携带信息时,不能最充分利用信号平面,这可由调制信号星座图中信号矢量端点的分布直观观察到。多进制振幅键控(MASK)调制时,矢

-

摘 要:DSP&FPGA技术在许多领域均有广泛的应用,特别是在无线通信领域里,由于具有极强的实时性,使其对信号进行实时处理成为可能。本文首先对DSP与FPGA作了比较,对DSP&FPGA在无线通信中的应用领域作了详细的分析,并对DSP&FPGA的发展方向及其在未来无线通信中的应用发展作了展望。 关键词:

-

关键字: WCDMA系统 DSP FPGA 引言 随着Internet的迅猛发展和各种无线业务需求的增加,目前以承载单一话音业务为主的无线通信网已经越来越不适应人们的需要,所以,以大容量、高数据率和承载多媒体业务为目的的第三代移动通信系统(IMT-2000)成为无线通

-

1 引言 OFDM(正交频分复用)是一种多载波数字调制技术,被公认为是一种实现高速双向无线数据通信的良好方法。在OFDM系统中,各子载波上数据的调制和解调是采用FFT(快速傅里叶变换)算法来实现的。因此在OFDM系统中,FFT的实现方案是一个关键因素。其运算精度和速度必须能够达到系统指标。对于一个有512个

-

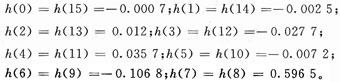

1 引 言 目前FIR滤波器的实现方法主要有3种:利用单片通用数字滤波器集成电路、DSP器件和可编程逻辑器件实现。单片通用数字滤波器使用方便,但由于字长和阶数的规格较少,不能完全满足实际需要。使用DSP器件实现虽然简单,但由于程序顺序执行,执行速度必然不快。 FPGA有着规整的内部逻辑阵列和丰富的

按照发布时间排序